# **EEE3571 Electronic Engineering I**

### **Lecture 6:** Field Effect Transistors

May 2022

daliso.banda@unza.zm

# References

Our main reference text books in this course are

- [1] Neil S., Electronics: A Systems Approach, 4th edition, 2009, Pearson Education Limited, ISBN 978-0-273-71918-2.

- [2] Boylestad R. L., Nashelsky L., Electronic Devices and Circuit Theory, 11<sup>th</sup> Ed, 2013, Prentice-Hall, ISBN 978-0-13-262226-4.

- [3] Smith R. J., Dorf R. C., Circuits Devices and Systems, 5<sup>th</sup> Ed., 2004, John Wiley, ISBN ISBN 9971-51-172-X.

However, feel free to use pretty much any additional text which you might find relevant to our course.

# **Learning Objectives**

At the end of the lecture 6 on Field Effect Transistors, you ought to:

- Become familiar with the construction and operating characteristics of Junction Field Effect (JFET), Metal-Oxide Semiconductor FET (MOSFET). Metal-Semiconductor FET (MESFET) transistors will not be covered.

- 2) Be able to sketch the transfer characteristics from the drain characteristics of a JFET and MOSFET transistor.

- 3) Understand the key parameters provided on the specification sheet for each type of FET.

- 4) Be aware of the differences between the dc analysis of the various types of FETs.

# **6.1 Introduction**

- □ The Field Effect Transistor (FET) is a three-terminal device used for a wide range of applications, similar to those for BJTs.

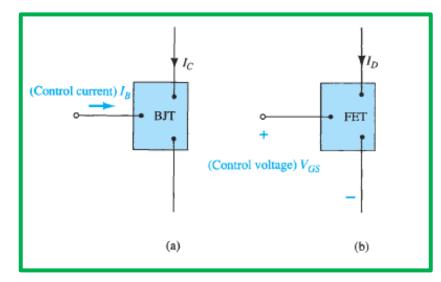

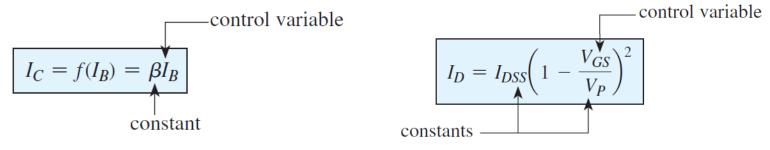

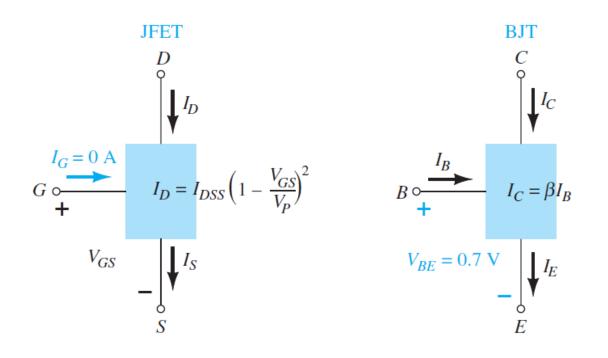

- □ The primary difference between FETs and BJTs is the fact that: the BJT is a current-controlled device as depicted in Fig. 6.1a, whereas the JFET is a voltage-controlled device as shown in Fig. 6.1b.

**Figure 6.1**: (a) Current-controlled; (b) voltage-controlled amplifiers.

- ☐ Just as there are *npn* and *pnp* BJTs, there *n*-channel and *p*-channel FETs.

- □ It is worth noting that while BJTs are bipolar, FETs are unipolar, as they depend wholly on either electron (*n*-channel) or hole (*p*-channel) condition.

- For FETs the electric field is established by charges present, which controls the conduction path of the output circuit.

# **6.1 Introduction Cont'd**

- One of the most important characteristics of the FET is its high input impedance.

- This is a critical characteristic in the design of linear ac amplifiers.

- Quiet on the contrary, typical ac voltage gain for BJT amplifiers are a great deal more than for FETs.

- However, FETs are more temperature stable than BJTs, and FETs are usually smaller than BJTs, making them particularly useful in integrated-circuit (IC) chips

- □ Three types to be discussed are: the junction field-effect transistor (JFET), the metal-oxide-semiconductor field effect transistor (MOSFET), and the metal-semiconductor field effect transistor (MESFET).

**Figure 6.3**: Water analogy for the JFET control mechanism.

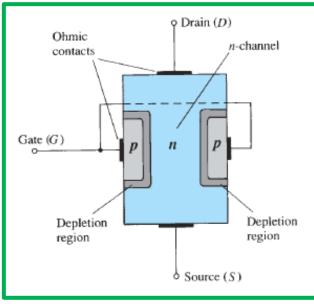

**Figure 6.2**: Junction field-effect transistor (JFET).

For the JFET the *n*-channel device will be prominently discussed.

- □ For the JFET the *n*-channel device will be prominently discussed.

- ☐ In the absence of applied potentials the JFET has two *p*-*n* junctions under no bias

### $V_{GS} = 0 V, V_{DS}$ Some Positive Value

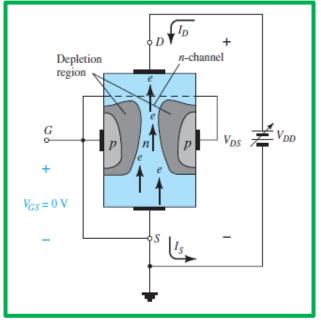

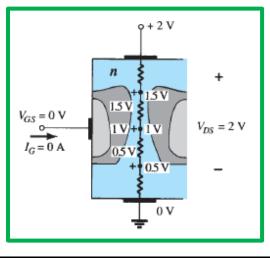

□ In Fig. 6.4, a positive voltage V is applied across the channel and the gate is connected directly to the source to establish the condition  $V_{GS} = 0$  V.

**Figure 6.4**: JFET at  $V_{GS} = 0$  V and  $V_{DS} > 0$  V.

□ Notice that as the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons are drawn to the drain terminal, establishing the conventional current  $I_D$ .

The path of charge flow shows that  $I_D = I_S$ .

**Figure 6.5**: Varying reverse-bias potentials across the *p*-*n* junction of an *n*-channel JFET.

- $\Box$  The depletion region is wider near the top of both *p*-type materials.

- □ Assuming a uniform resistance in the *n*-channel, we can break it down into divisions depicted in Fig. 6.5. Thus,  $I_D$  establishes voltage drops indicated.

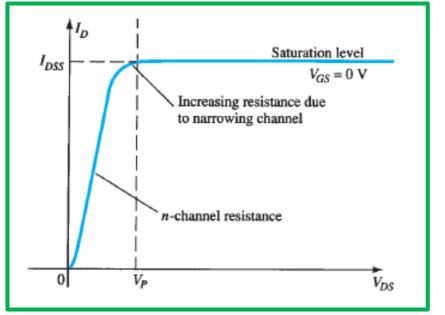

**Figure 6.6**:  $I_D$  versus  $V_{DS}$  for  $V_{GS} = 0$  V.

- ❑ Notice that the upper region of the *p*type material will be reverse-biased by about 1.5 V, with the lower region only reversed-biased by 0.5 V.

- Recall that the greater the applied reverse bias, the wider is the depletion region.

- □ An important characteristic of the JFET is that  $I_G = 0$  A.

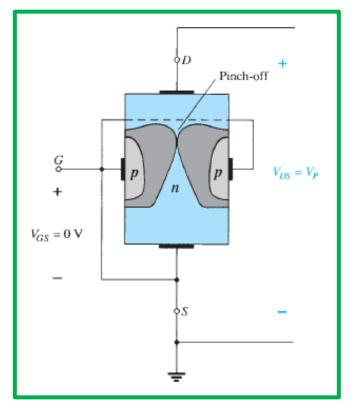

Figure 6.7: Pinch-off  $(V_{GS} = 0 \text{ V}, V_{DS} = V_p).$

- Beyond the pinch-off voltage,  $I_D$  maintains a saturation level as  $I_{DSS}$  in Fig. 6.6.

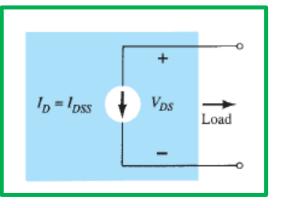

- □ In essence, once  $V_{DS} > V_p$  the JFET has the characteristics of a current source.

- □ Thus,  $I_{DSS}$  is the maximum drain current for a JFET and is defined by conditions  $V_{GS} = 0$  V and  $V_{DS} > |V_p|$ .

**Figure 6.8**: current source equivalent for  $V_{GS} = 0$  V,  $V_{DS} > V_p$ .

**Figure 6.9**: Application of a negative voltage to the gate of a JFET.

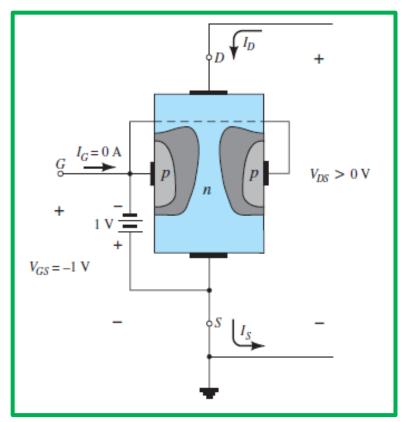

### $V_{GS} < 0 \text{ V}$

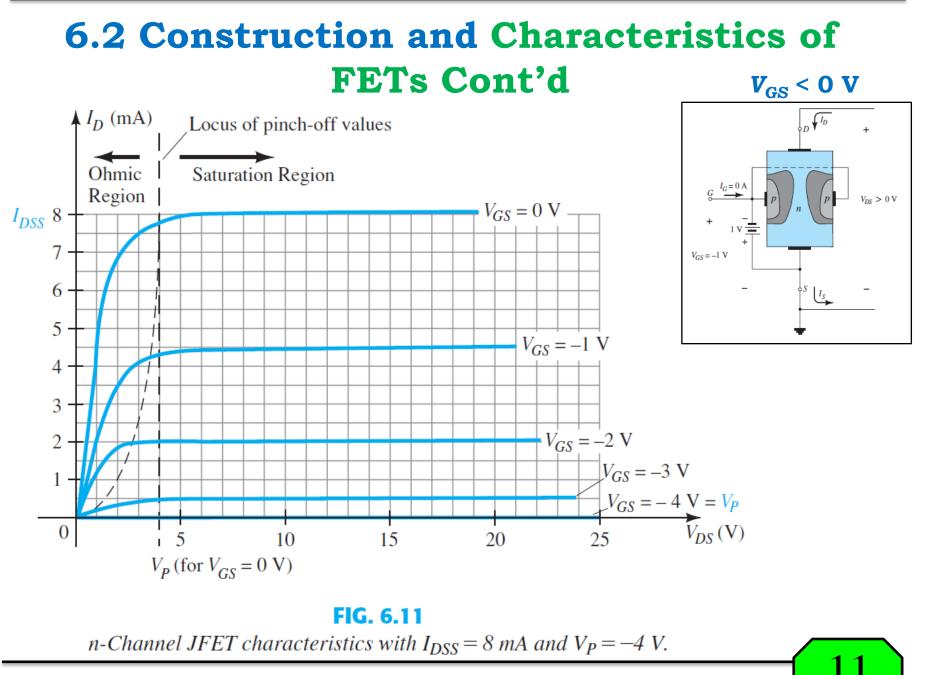

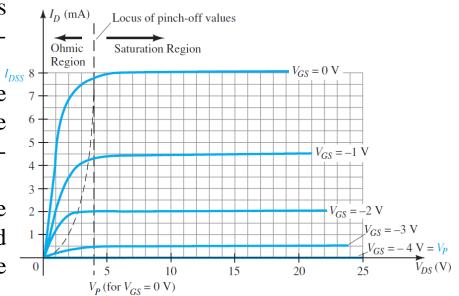

- □ Here, various curves of  $I_D$  versus  $V_{DS}$  for various levels of  $V_{GS}$  can be developed for the JFET.

- ☐ The level of  $V_{GS}$  that results in  $I_D = 0$ mA is defined by  $V_{GS} = V_p$ , with  $V_p$  being a negative for *n*-channel devices and a positive voltage for *p*-channel JFETs.

- □ On most specification sheets the pinch-off voltage is specified as  $V_{GS(off)}$  rather than  $V_P$ .

The region to the left of the pinch-off locus is referred to as the *ohmic or voltagecontrolled resistance* region.

□In this region the JFET can actually be employed as a variable resistor; whose resistance is controlled by the applied gate-tosource voltage.

□Note the slope of each curve and therefore the resistance of the device between drain and source for  $V_{DS} < V_P$  are a function of the applied voltage  $V_{GS}$ .

$\Box$ As  $V_{GS}$  becomes more and more negative, the slope of each curve becomes more and more horizontal, corresponding to an increasing resistance level.

The following equation provides a good first approximation to the resistance level in terms of the applied voltage  $V_{GS}$ :

$$r_d = \frac{r_o}{\left(1 - V_{GS}/V_P\right)^2}$$

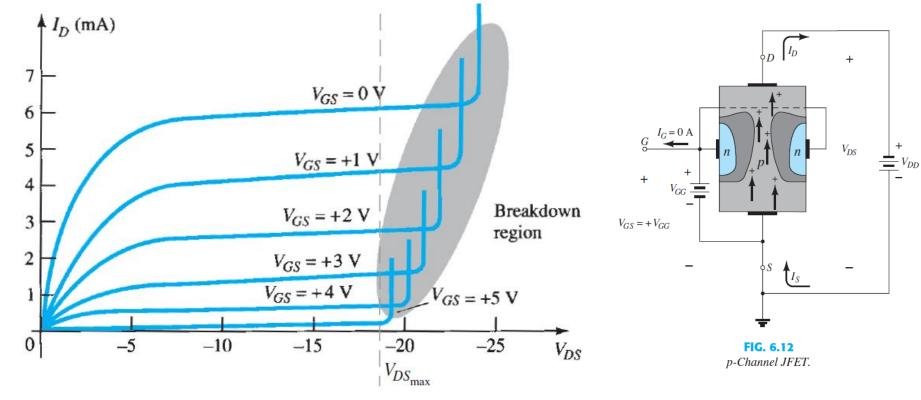

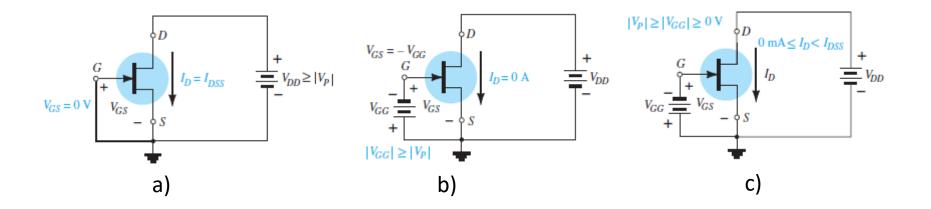

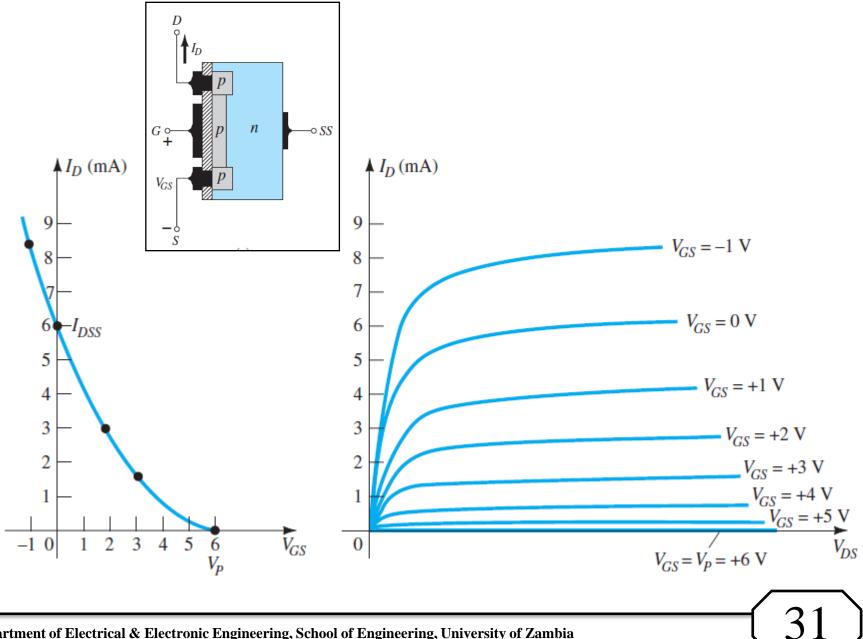

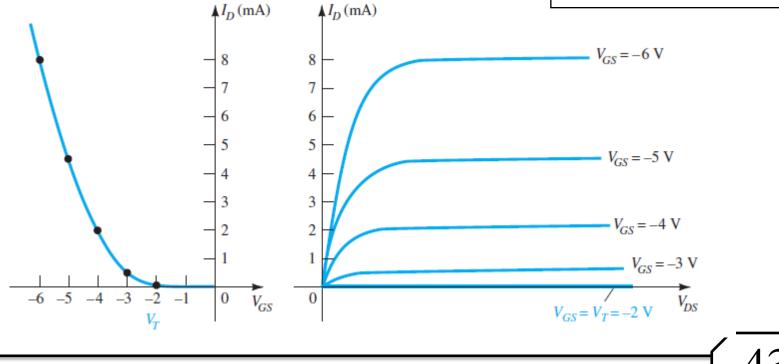

### **Construction of P-Channel JFET**

The p -channel JFET is constructed in exactly the same manner as the n -channel device of but with a reversal of the p - and n -type materials The defined current directions are reversed, as are the actual polarities for the voltages  $V_{GS}$  and  $V_{DS}$ .

□For the p -channel device, the channel will be constricted by increasing positive voltages from gate to source and the double-subscript notation for  $V_{DS}$  will result in negative voltages for  $V_{DS}$  on the characteristics.

FIG. 6.12 p-Channel JFET.

### **Construction of P-Channel JFET**

### FIG. 6.13

*p*-Channel JFET characteristics with  $I_{DSS} = 6$  mA and  $V_P = +6$  V.

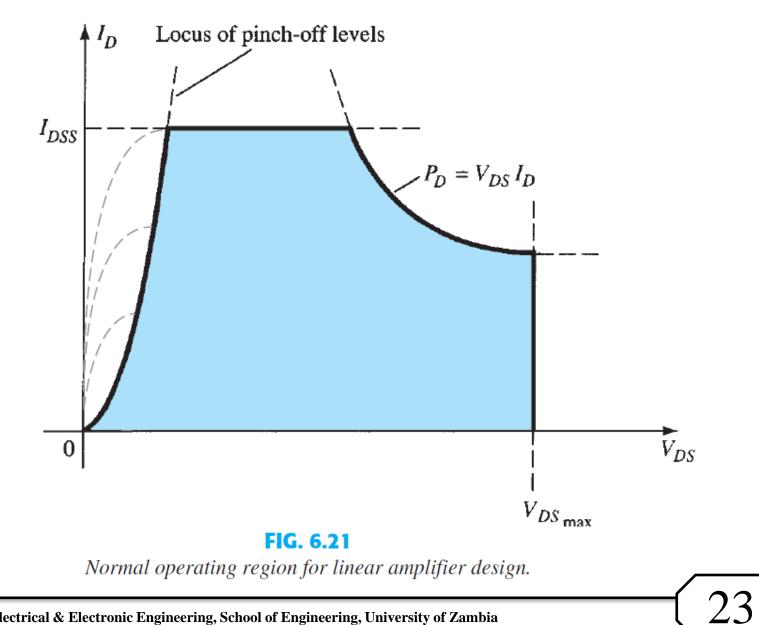

$\Box$ At high levels of  $V_{DS}$  the curves suddenly rise to levels that seem unbounded.

This vertical rise is an indication that breakdown has occurred and the current through the channel is now limited solely by the external circuit.

□This also occurs for the n -channel device if sufficient voltage is applied.

This region can be avoided if the level of  $V_{DSmax}$  is noted on the specification sheet and the design is such that  $V_{DS} < V_{DSmax}$  for all values of  $V_{GS}$ .

### **Construction of P-Channel JFET**

### FIG. 6.13

*p*-Channel JFET characteristics with  $I_{DSS} = 6$  mA and  $V_P = +6$  V.

$\Box$ At high levels of  $V_{DS}$  the curves suddenly rise to levels that seem unbounded.

This vertical rise is an indication that breakdown has occurred and the current through the channel is now limited solely by the external circuit.

□This also occurs for the n -channel device if sufficient voltage is applied.

This region can be avoided if the level of  $V_{DSmax}$  is noted on the specification sheet and the design is such that  $V_{DS} < V_{DSmax}$  for all values of  $V_{GS}$ .

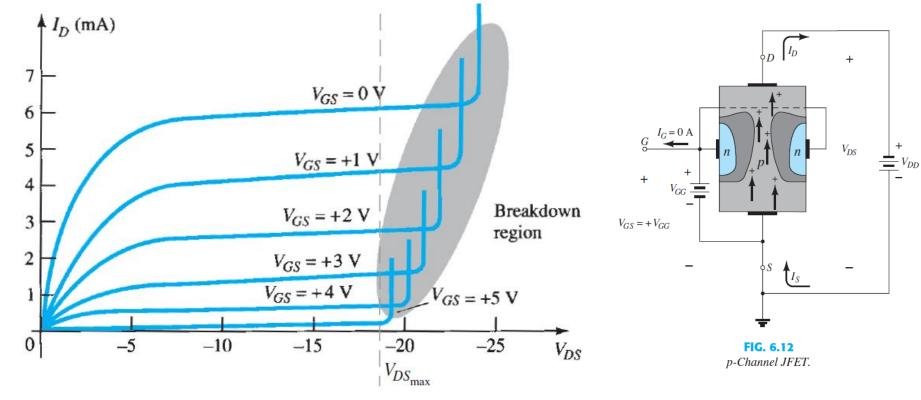

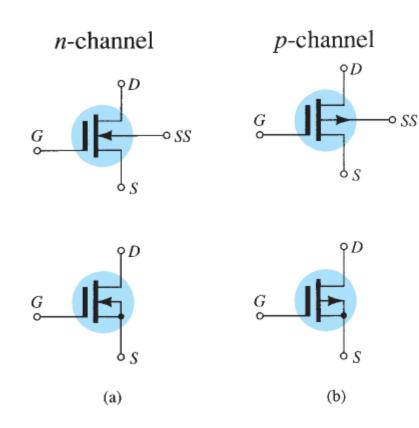

### **JFET Symbols**

The arrow is pointing in for the *n*-channel device of Fig. 6.14a to represent the direction in which  $I_G$  would flow if the *p*-*n* junction were forward-biased.

□For the p -channel device the only difference in the symbol is the direction of the arrow in the symbol.

### FIG. 6.14

JFET symbols: (a) n-channel; (b) p-channel.

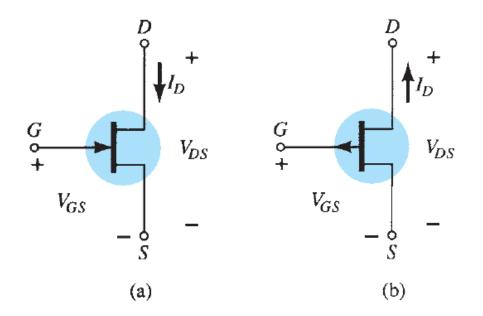

### **Summary of JFET Characteristics**

### n-Channel JFET:

- a) The maximum current is defined as  $I_{DSS}$  and occurs when  $V_{GS} = 0$  V and  $V_{DS} \ge V_P$ .

- b) For gate-to-source voltages  $V_{GS} < V_P$  (or more negative than the pinch-off level), the drain current  $I_D = 0$ A.

- c) For all levels of  $V_P < V_{GS} < 0$ V,  $I_D$  will range between  $I_{DSS}$  and 0A.

A similar list can be developed for p-channel JFETs.

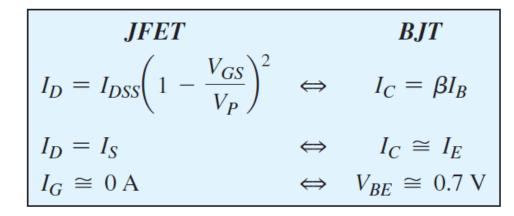

### **JFET Transfer Characteristics**

- □ For the BJT transistor the output current  $I_C$  and the input controlling current  $I_B$  are related by beta, which was considered constant for the analysis to be performed.

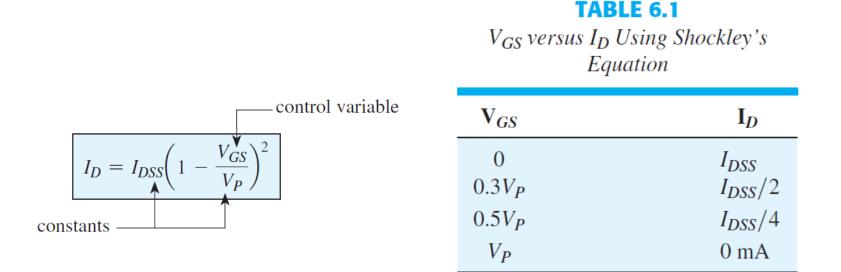

- ☐ The relationship between  $I_D$  and  $V_{GS}$  is defined by Shockley's equation.

- □ For the dc analysis to be performed a graphical rather than a mathematical approach will in general be more direct and easier to apply.

- □ The graphical approach, however, will require a plot of Shockley's equation to represent the device and a plot of the network equation relating the same variables.

- $\rightarrow$  The solution is defined by the point of intersection of the two curves.

- □ It is important to keep in mind when applying the graphical approach that the device characteristics will be unaffected by the network in which the device is employed.

### **JFET Transfer Characteristics**

□ Since the transfer curve must be plotted so frequently, a shorthand method for plotting the curve quickly, efficiently and with acceptable degree of accuracy is used:

### **JFET Transfer Characteristics**

**EXAMPLE 6.1** Sketch the transfer curve defined by  $I_{DSS} = 12$  mA and  $V_P = -6$  V.

**Solution:** Two plot points are defined by

and

$$I_{DSS} = \mathbf{12} \mathbf{mA}$$

and  $V_{GS} = \mathbf{0} \mathbf{V}$

$I_D = \mathbf{0} \mathbf{mA}$  and  $V_{GS} = V_P$

At  $V_{GS} = V_P/2 = -6 \text{ V}/2 = -3 \text{ V}$  the drain current is determined by  $I_D = I_{DSS}/4 = 12 \text{ mA}/4 = 3 \text{ mA}$ . At  $I_D = I_{DSS}/2 = 12 \text{ mA}/2 = 6 \text{ mA}$  the gate-to-source voltage is determined by  $V_{GS} \approx 0.3V_P = 0.3(-6 \text{ V}) = -1.8 \text{ V}$ . All four plot points are well defined on Fig. 6.18 with the complete transfer curve.

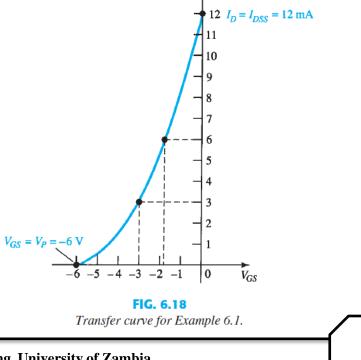

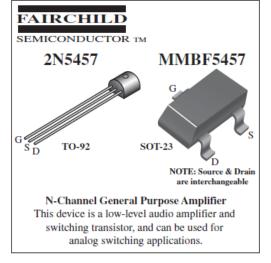

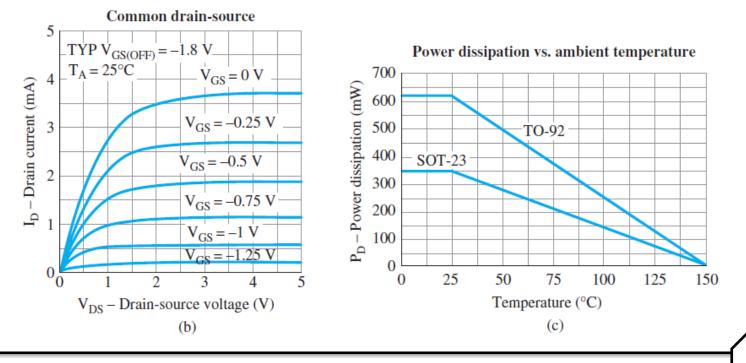

### **JFET Specification Sheet**

#### ABSOLUTE MAXIMUM RATINGS

| Symbol          | Parameter                                           | Value       | Units |

|-----------------|-----------------------------------------------------|-------------|-------|

| V <sub>DS</sub> | Drain-Source Voltage                                | 25          | V     |

| V <sub>DG</sub> | Drain-Gate Voltage                                  | 25          | v     |

| V <sub>GS</sub> | Gate-Source Voltage                                 | -25         | V     |

| I <sub>GF</sub> | Forward Gate Current                                | 10          | mA    |

| $T_j, T_{stg}$  | Operating and Storage Junction<br>Temperature Range | -55 to +150 | °C    |

2

#### THERMAL CHARACTERISTICS

| Symbol           | Characteristic                                | M          | Units      |             |

|------------------|-----------------------------------------------|------------|------------|-------------|

|                  | Characteristic                                | 2N5457     | *MMBF5457  | Units       |

| P <sub>D</sub>   | Total Device Dissipation<br>Derate above 25°C | 625<br>5.0 | 350<br>2.8 | mW<br>mW/°C |

| R <sub>0JC</sub> | Thermal Resistance, Junction to Case          | 125        |            | °C/W        |

| $R_{\theta JA}$  | Thermal Resistance, Junction to Ambient       | 357        | 556        | °C/W        |

#### ELECTRICAL CHARACTERISTICS $T_A = 25^{\circ}C$ unless otherwise noted

| Symbol P | Parameter | Test Conditions | Min | Тур | Max | Units |

|----------|-----------|-----------------|-----|-----|-----|-------|

|----------|-----------|-----------------|-----|-----|-----|-------|

#### OFF CHARACTERISTICS

| V <sub>(BR)GSS</sub> | Gate-Source Breakdown Voltage | $I_{G} = 10 \ \mu A, V_{DS} = 0$                                                                        | -25  |      |              | v        |

|----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------|------|------|--------------|----------|

| I <sub>GSS</sub>     | Gate Reverse Current          | $V_{GS} = -15 \text{ V}, V_{DS} = 0$<br>$V_{GS} = -15 \text{ V}, V_{DS} = 0, T_A = 100^{\circ}\text{C}$ |      |      | -1.0<br>-200 | nA<br>nA |

| V <sub>GS(off)</sub> | Gate-Source Cutoff Voltage    | $V_{DS} = 15 \text{ V}, I_D = 10 \text{ nA}$ 5457                                                       | -0.5 |      | -6.0         | v        |

| V <sub>GS</sub>      | Gate-Source Voltage           | $V_{DS} = 15 \text{ V}, I_D = 100 \ \mu\text{A}$ 5457                                                   |      | -2.5 |              | v        |

### **JFET Specification Sheet**

ON CHARACTERISTICS

| I <sub>DSS</sub> | Zero-Gate Voltage Drain Current | $V_{\rm DS} = 15 \text{ V}, V_{\rm GS} = 0$ | 5457 | 1.0 | 3.0 | 5.0 | mA |

|------------------|---------------------------------|---------------------------------------------|------|-----|-----|-----|----|

|------------------|---------------------------------|---------------------------------------------|------|-----|-----|-----|----|

#### SMALL SIGNAL CHARACTERISTICS

| g <sub>fs</sub>  | Forward Transfer Conductance | $V_{DS} = 15 \text{ V}, V_{GS} = 0, f = 1.0 \text{ kHz}$ 5457    | 1000 |     | 5000 | $\mu$ mhos |

|------------------|------------------------------|------------------------------------------------------------------|------|-----|------|------------|

| g <sub>os</sub>  | Output Conductance           | $V_{DS}$ = 15 V, $V_{GS}$ = 0, f = 1.0 MHz                       |      | 10  | 50   | μmhos      |

| C <sub>iss</sub> | Input Capacitance            | $V_{DS} = 15 \text{ V}, V_{GS} = 0, \text{ f} = 1.0 \text{ MHz}$ |      | 4.5 | 7.0  | pF         |

| C <sub>rss</sub> | Reverse Transfer Capacitance | $V_{DS} = 15 \text{ V}, V_{GS} = 0, f = 1.0 \text{ MHz}$         |      | 1.5 | 3.0  | pF         |

| NF               | Noise Figure                 | $V_{DS} = 15 \text{ V}, V_{GS} = 0, f = 1.0 \text{ kHz},$        |      |     | 3.0  | dB         |

|                  |                              | $R_G = 1.0$ megohm, BW = 1.0 Hz                                  |      |     |      |            |

(a)

22

### **JFET Operating Region**

### **JFET Specification Sheet**

- □ The electrical characteristics include the level of  $V_P$  in the "off" characteristics,  $I_{DSS}$  in the "on" characteristics.

- $\Box$   $V_P = V_{GS(off)}$  has a range from -0.5 V to -6.0 V and

- $\Box$   $I_{DSS}$  from 1 mA to 5 mA.

- □ The fact that both will vary from device to device with the same nameplate identification must be considered in the design process.

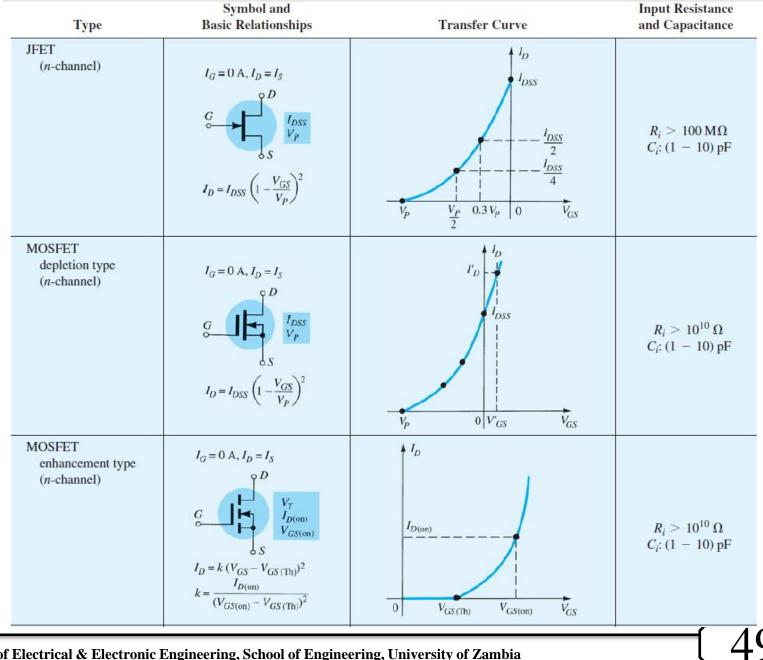

### **Comparison of JFET with BJT**

25

### **Introduction to MOSFETS**

- □ There are three types of FETs: JFETs, MOSFETs, and MESFETs.

- □ MOSFETs are further broken down into depletion type and enhancement type.

- □ The terms depletion and enhancement define their basic mode of operation.

- □ The name MOSFET stands for metal–oxide–semiconductor fieldeffect transistor (name will make more sense when studying structure).

- □ In this section we examine the depletion-type MOSFET, which has characteristics similar to those of a JFET between cutoff and saturation at  $I_{DSS}$ ,

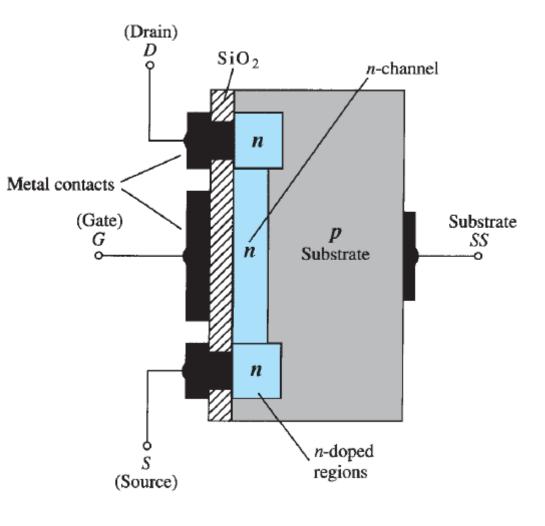

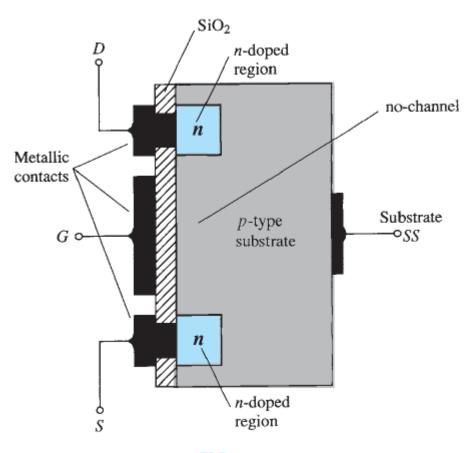

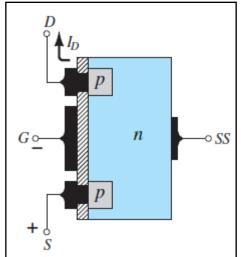

### **Structure of n-Channel Depletion-type MOSFETS**

- □ A slab of p -type material is formed from a silicon base.

- □ In some cases the substrate is internally connected to the source terminal.

- The source and drain terminals are connected through metallic contacts to n-doped regions linked by an nchannel.

- □ The gate is also connected to a metal contact surface but remains insulated from the n-channel by a very thin silicon dioxide (SiO<sub>2</sub>) layer.

- □ This accounts for the very desirable high input impedance of the device.

- □ The input resistance of a MOSFET is usually more than that of a typical JFET

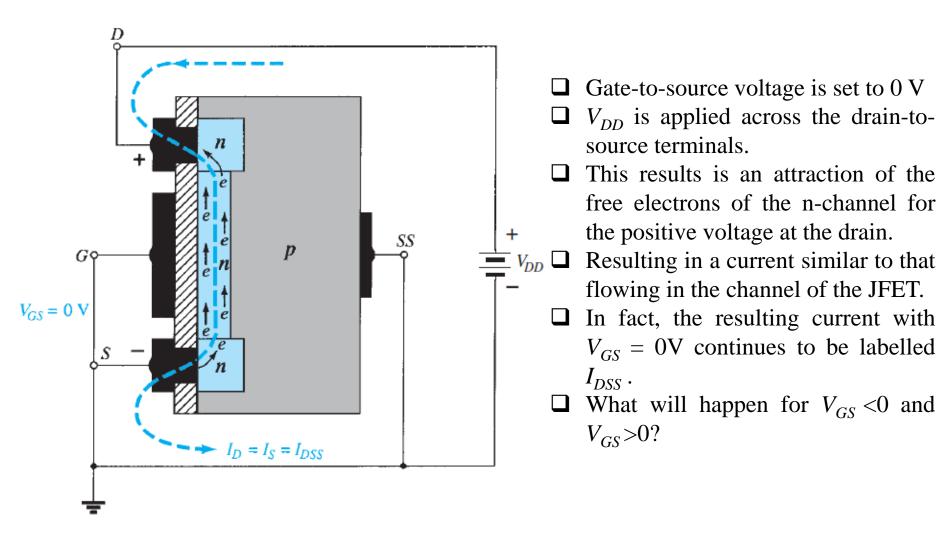

### **Basic Operation and Characteristics** n-Channel Depletion-type MOSFETS

### **Basic Operation and Characteristics** n-Channel Depletion-type MOSFETS

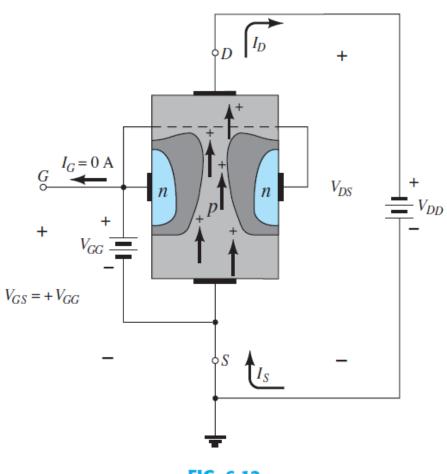

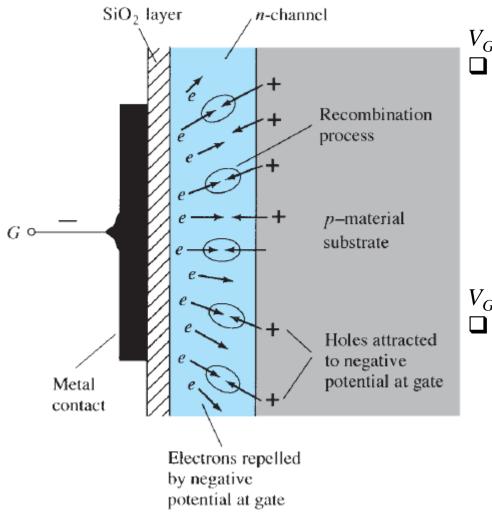

- $V_{GS} < 0$

- The negative potential at the gate will tend to pressure electrons toward the p -type substrate (like charges repel) and attract holes from the p -type substrate

- → a level of recombination between electrons and holes will occur that will reduce the number of free electrons in the n -channel available for conduction.

- $V_{GS} > 0$

- The positive gate will draw additional electrons (free carriers) from the *p*-type substrate due to the reverse leakage current and establish new carriers through the collisions resulting between accelerating particles.

### **Basic Operation and Characteristics** n-Channel Depletion-type MOSFETS

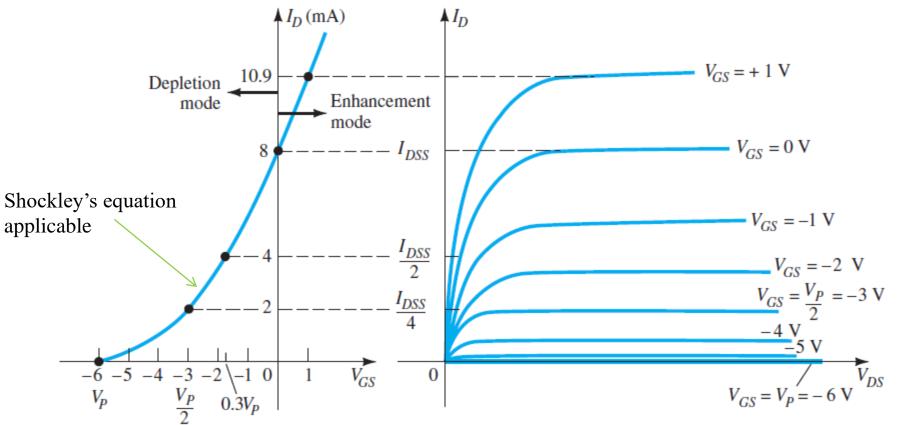

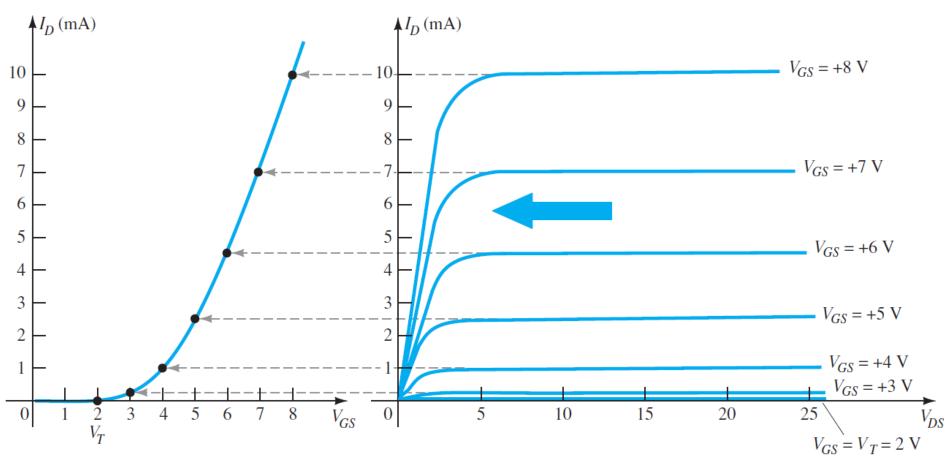

Drain and transfer characteristics for an n-channel depletion-type MOSFET.

Application of a positive gate-to-source voltage has "enhanced" the level of free carriers in the channel compared to that encountered with  $V_{GS}=0$

□ For this reason the region of positive gate voltages on the drain or transfer characteristics is often referred to as the *enhancement* region , with the region between cutoff and the saturation level of  $I_{DSS}$  referred to as the *depletion* region.

### **p**-Channel Depletion-Type MOSFET

### **Depletion-Type MOSFET Symbols**

3

### **MOSFET Specification Sheet**

### 2N3797 MOSFET LOW-POWER AUDIO 3 Drain Gate 2 O 1 Source N-CHANNEL - DEPLETION

37

#### MAXIMUM RATINGS

| Rating                                                                | Symbol           | Value       | Unit        |

|-----------------------------------------------------------------------|------------------|-------------|-------------|

| Drain–Source Voltage<br>2N3797                                        | V <sub>DS</sub>  | 20          | Vdc         |

| Gate-Source Voltage                                                   | V <sub>GS</sub>  | ±10         | Vdc         |

| Drain Current                                                         | ID               | 20          | mAdc        |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C | PD               | 200<br>1.14 | mW<br>mW/°C |

| Junction Temperature Range                                            | Тյ               | +175        | °C          |

| Storage Channel Temperature Range                                     | T <sub>stg</sub> | -65 to +200 | °C          |

### **MOSFET Specification Sheet**

#### **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ unless otherwise noted)

|        | Symbol               | Min                                                                                  | Тур                                                                                                 | Max                                                    | Unit                                                   |

|--------|----------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

|        |                      |                                                                                      |                                                                                                     |                                                        |                                                        |

| 2N3797 | V <sub>(BR)DSX</sub> | 20                                                                                   | 25                                                                                                  | _                                                      | Vdc                                                    |

|        | l <sub>GSS</sub>     | -                                                                                    | -                                                                                                   | 1.0<br>200                                             | pAdc                                                   |

| 2N3797 | V <sub>GS(off)</sub> | _                                                                                    | -5.0                                                                                                | -7.0                                                   | Vdc                                                    |

|        | I <sub>DGO</sub>     | -                                                                                    | -                                                                                                   | 1.0                                                    | pAdc                                                   |

|        |                      |                                                                                      |                                                                                                     |                                                        |                                                        |

| 2N3797 | I <sub>DSS</sub>     | 2.0                                                                                  | 2.9                                                                                                 | 6.0                                                    | mAdc                                                   |

|        | I <sub>D(on)</sub>   | 9.0                                                                                  | 14                                                                                                  | 18                                                     | mAdc                                                   |

|        | 2N3797               | 2N3797<br>V(BR)DSX<br>IGSS<br>2N3797<br>VGS(off)<br>IDGO<br>IDSS<br>2N3797<br>ID(on) | 2N3797 V(BR)DSX 20   IGSS -   2N3797 IGSS   2N3797 VGS(off)   IDGO -   IDGO -   IDSS 2.0   ID(on) I | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

### **MOSFET Specification Sheet**

#### SMALL-SIGNAL CHARACTERISTICS

| Forward Transfer Admittance                                                                |        | y <sub>fs</sub> |      |      |      | μmhos |

|--------------------------------------------------------------------------------------------|--------|-----------------|------|------|------|-------|

| $(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1.0 \text{ kHz})$                                 | 2N3797 |                 | 1500 | 2300 | 3000 |       |

| $(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1.0 \text{ MHz})$                                 | 2N3797 |                 | 1500 | -    | -    |       |

| Output Admittance                                                                          |        | Y <sub>os</sub> |      |      |      | μmhos |

| $(1_{DS} = 10 \text{ V}, \text{ V}_{GS} = 0, \text{ f} = 1.0 \text{ kHz})$                 | 2N3797 |                 | -    | 27   | 60   |       |

| Input Capacitance                                                                          |        | Ciss            |      |      |      | pF    |

| $(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1.0 \text{ MHz})$                                 | 2N3797 |                 | -    | 6.0  | 8.0  |       |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 0, f = 1.0 MHz) |        | $C_{rss}$       | 275  | 0.5  | 0.8  | pF    |

| FUNCTIONAL CHARACTERISTICS                                                                 |        |                 |      |      | -    |       |

| Noise Figure                                                                               |        | NF              | -    | 3.8  |      | dB    |

Noise Figure  $(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1.0 \text{ kHz}, R_S = 3 \text{ megohms})$ NF - 3.8

(1) This value of current includes both the FET leakage current as well as the leakage current associated with the test socket and fixture when measured under best attainable conditions.

### **Enhancement - Type MOSFET**

- □ There are some similarities in construction and mode of operation between depletion type and enhancement-type MOSFETs.

- □ But, the characteristics of the enhancement-type MOSFET are quite different from anything obtained thus far.

- □ The transfer curve is not defined by Shockley's equation, and the drain current is now cut off until the gate-to source voltage reaches a specific magnitude.

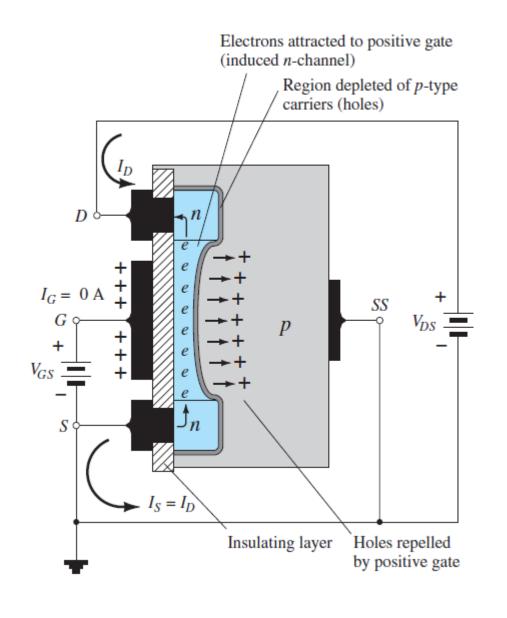

FIG. 6.32 n-Channel enhancement-type MOSFET.

- □ A slab of p -type material is formed from a silicon base and is again referred to as the substrate.

- As with the depletion-type MOSFET, the substrate is sometimes internally connected to the source terminal.

- □ The source and drain terminals are again connected through metallic contacts to n-doped regions.

- □ But note the absence of a channel between the two n -doped regions.

- □ The SiO<sub>2</sub> layer is still present to isolate the gate metallic platform from the region between the drain and source.

- □ If  $V_{GS} = 0V$  and  $V_{DS} > 0V$  the absence of an n-channel will result in a current of effectively 0A (quite different from the depletion-type MOSFET and JFET)

- □ with  $V_{GS}$  >0 and  $V_{DS}$  >0 establishing the drain and the gate at a positive potential with respect to the source.

- □ Positive potential at the gate will pressure the holes in the *p*-substrate along the edge of the  $SiO_2$  to enter deeper into the *p*-substrate.

- □ Resulting in a depletion region near the SiO<sub>2</sub> insulating layer void of holes.

- □ However, the electrons in the *p*-substrate will be attracted to the positive gate and accumulate in the at the surface of the SiO<sub>2</sub> layer.

- □ The SiO<sub>2</sub> layer and its insulating qualities will prevent the negative carriers from being absorbed at the gate terminal.

- □ Once  $V_{GS}$  is large enough the induced n-type region can support a measurable current.

- □ The level of  $V_{GS}$  that results in the significant increase in drain current is called the threshold voltage,  $V_T$ .

- □ On specification sheets it is referred to as  $V_{GS(Th)}$ .

- □ Since the channel is nonexistent with  $V_{GS} = 0$  V and "enhanced" by the application of a positive gate-tosource voltage,

- → this type of MOSFET is called enhancement-type MOSFET.

- □ Both depletion-and enhancement type MOSFETs have enhancementtype regions, but the label was applied to the latter since it is its only mode of operation.

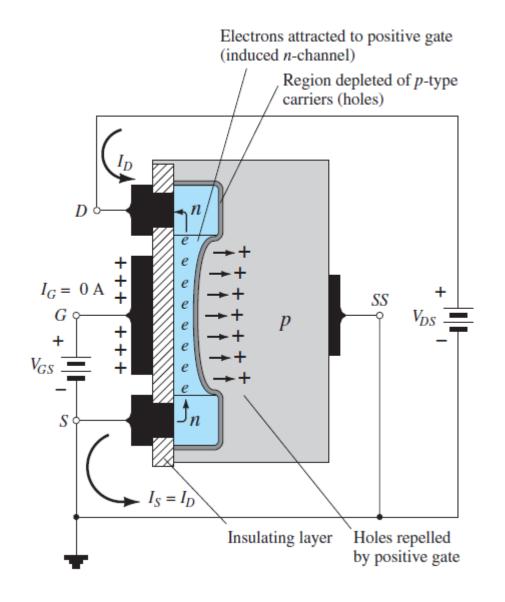

- □ If we hold  $V_{GS}$  constant and increase the level of  $V_{DS}$ , the drain current will eventually reach a saturation level.

- □ "This reduction in gate-to-drain voltage will in turn reduce the attractive forces for free carriers (electrons) in this region of the induced Channel" [really ?]

- Causing a reduction in the effective channel width.

- □ Eventually, the channel will be reduced to the point of pinch-off and resulting in saturation.

- □ The levelling off of  $I_D$  is due to a pinching-off process depicted by the narrower channel at the drain end of the induced channel.

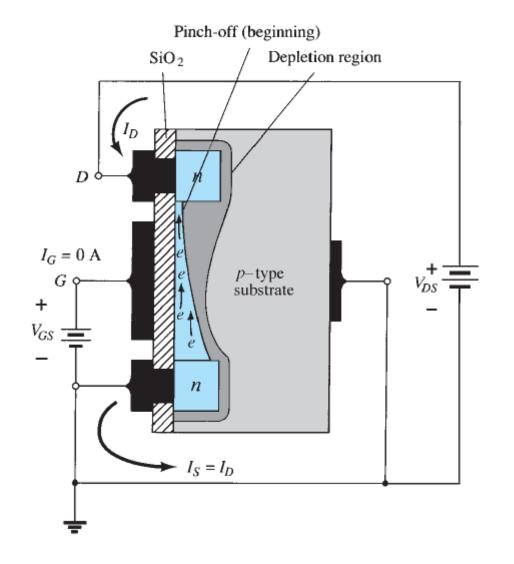

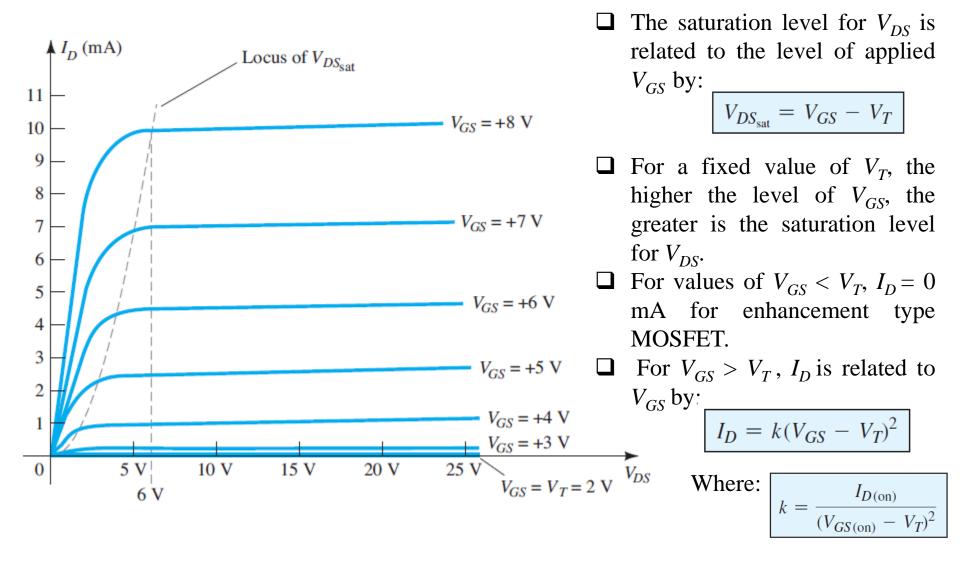

### Drain characteristics of an *n*-channel enhancementtype MOSFET

### Sketching the transfer characteristics for an nchannel enhancement-type MOSFET from the drain characteristics

☐ For the dc analysis of enhancement-type MOSFETs, the transfer characteristics will again be the characteristics to be employed in the graphical solution.

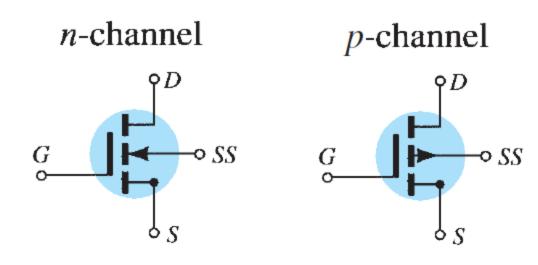

#### **p**-Channel Enhancement-Type MOSFETs

- □ The construction of a *p*-channel enhancementtype MOSFET is exactly the reverse of the n-Channel variant.

- □ The terminals remain as identified, but all the voltage polarities and the current directions are reversed

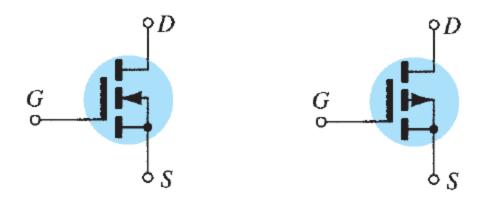

# Symbols for *n* and *p*-channel enhancement-type MOSFETs

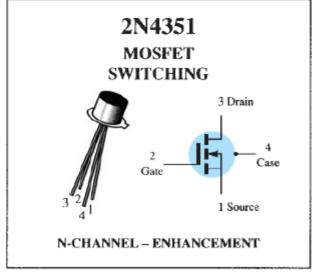

#### 2N4351 Motorola n-channel enhancement-type **MOSFET**

| Rating                                                                | Symbol          | Value       | Unit        |

|-----------------------------------------------------------------------|-----------------|-------------|-------------|

| Drain-Source Voltage                                                  | V <sub>DS</sub> | 25          | Vdc         |

| Drain-Gate Voltage                                                    | V <sub>DG</sub> | 30          | Vdc         |

| Gate-Source Voltage*                                                  | V <sub>GS</sub> | 30          | Vdc         |

| Drain Current                                                         | ID              | 30          | mAdc        |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C | PD              | 300<br>1.7  | mW<br>mW/°C |

| Junction Temperature Range                                            | Tj              | 175         | °С          |

| Storage Temperature Range                                             | Tsig            | -65 to +175 | °C          |

\* Transient potentials of ± 75 Volt will not cause gate-oxide failure.

#### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C unless otherwise noted.)

| Characteristic                                                                                                                           | Symbol               | Min | Max      | Unit         |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|----------|--------------|

| OFF CHARACTERISTICS                                                                                                                      |                      |     |          |              |

| Drain-Source Breakdown Voltage<br>( $I_D = 10 \ \mu A, V_{GS} = 0$ )                                                                     | V <sub>(BR)DSX</sub> | 25  | -        | Vdc          |

| Zero-Gate-Voltage Drain Current<br>$(V_{DS} = 10 \text{ V}, V_{GS} = 0) \text{ T}_A = 25^{\circ}\text{C}$<br>$T_A = 150^{\circ}\text{C}$ | I <sub>DSS</sub>     | -   | 10<br>10 | nAdc<br>µAdc |

| Gate Reverse Current<br>$(V_{GS} = \pm 15 \text{ Vdc}, V_{DS} = 0)$                                                                      | I <sub>GSS</sub>     |     | ± 10     | pAdc         |

#### 2N4351 Motorola n-channel enhancement-type MOSFET

| ON CHARACTERISTICS                                                                                  |                      |      |     |      |

|-----------------------------------------------------------------------------------------------------|----------------------|------|-----|------|

| Gate Threshold Voltage<br>( $V_{DS} = 10 \text{ V}, I_D = 10 \mu \text{A}$ )                        | V <sub>GS(Tb</sub> ) | 1.0  | 5   | Vdc  |

| Drain-Source On-Voltage<br>( $I_D = 2.0 \text{ mA}, V_{GS} = 10 \text{V}$ )                         | V <sub>DS(on)</sub>  | _    | 1.0 | v    |

| On-State Drain Current<br>( $V_{GS} = 10 \text{ V}, V_{DS} = 10 \text{ V}$ )                        | I <sub>D(on)</sub>   | 3.0  | -   | mAdc |

| SMALL-SIGNAL CHARACTERISTICS                                                                        |                      |      | _   |      |

| Forward Transfer Admittance<br>$(V_{DS} = 10 \text{ V}, I_D = 2.0 \text{ mA}, f = 1.0 \text{ kHz})$ | y <sub>fs</sub>      | 1000 | -   | µmho |

| Input Capacitance<br>$(V_{DS} = 10 \text{ V}, \text{ V}_{GS} = 0, \text{ f} = 140 \text{ kHz})$     | C <sub>iss</sub>     | -    | 5.0 | pF   |

| Reverse Transfer Capacitance<br>$(V_{DS} = 0, V_{GS} = 0, f = 140 \text{ kHz})$                     | C <sub>rss</sub>     | -    | 1.3 | pF   |

| Drain-Substrate Capacitance<br>$(V_{D(SUB)} = 10 \text{ V}, \text{ f} = 140 \text{ kHz})$           | C <sub>d(sub)</sub>  | -    | 5.0 | pF   |

| Drain-Source Resistance<br>( $V_{GS} = 10 \text{ V}, 1_D = 0, f = 1.0 \text{ kHz}$ )                | r <sub>ds(on)</sub>  | -    | 300 | ohms |

| SWITCHING CHARACTERISTICS                                                                           |                      |      |     |      |

| Tum-On Delay (Fig. 5)                                                                               | t <sub>d1</sub>      | -    | 45  | ns   |

| Turn-On Delay (Fig. 5)  |                                                                        | t <sub>d1</sub> | - | 45  | ns |

|-------------------------|------------------------------------------------------------------------|-----------------|---|-----|----|

| Rise Time (Fig. 6)      | $I_{\rm D} = 2.0 \text{ mAde}, V_{\rm DS} = 10 \text{ Vdc},$           | L,              | _ | 65  | ns |

| Turn-Off Delay (Fig. 7) | (V <sub>GS</sub> = 10 Vdc)<br>(See Figure 9; Times Circuit Determined) | t <sub>d2</sub> | - | 60  | ns |

| Fall Time (Fig. 8)      | (See Figure 2, Funds chean Determined)                                 | t <sub>f</sub>  | - | 100 | ns |

#### **MOSFET HANDLING**

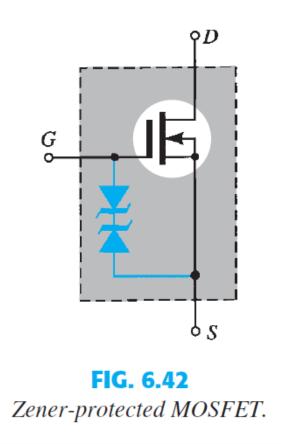

□ The thin SiO 2 layer between the gate and the channel of MOSFETs has the positive effect of providing a high-input-impedance characteristic for the device, but because of its extremely thin layer, it introduces a concern for its handling that was not present for the BJT or JFET transistors.

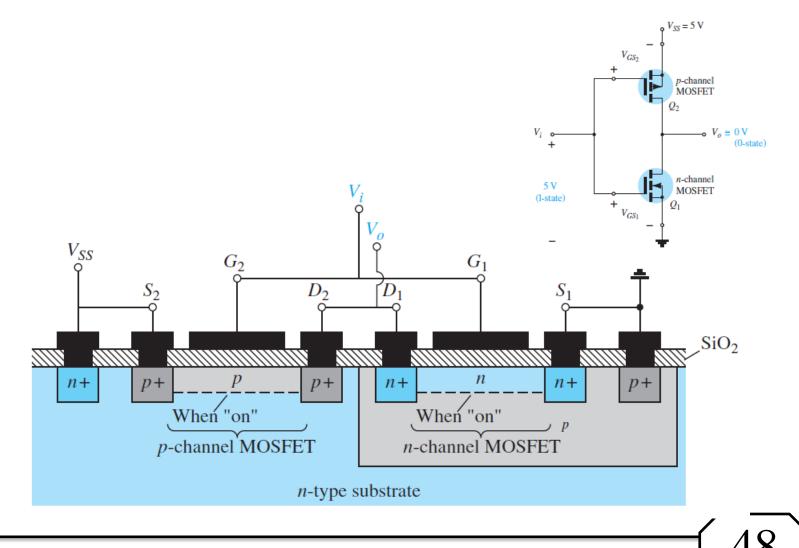

#### complementary MOSFET (CMOS)

□ A very effective logic circuit can be established by constructing a *p*-channel and an *n*-channel MOSFET on the same substrate. E.g CMOS NOT gate (inverter)

#### **JFET and MOSFETs**

## **End of Lecture 6**

# Thank you for your attention!